## ADAPTIVE AND ENERGY-EFFICIENT MANAGEMENT FOR HETEROGENEOUS MULTI-CORE ARCHITECTURES

# Dissertation

zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.)

> vorgelegt an der Technischen Universität Dresden Fakultät Informatik

> > eingereicht von

# **Robert Khasanov**

geboren am 16.01.1990 in Tschaikowski, UdSSR

## Gutachter:

Prof. Dr.-Ing. Jeronimo Castrillon Technische Universität Dresden

Prof. Dr.-Ing. Jürgen Teich Friedrich-Alexander-Universität Erlangen-Nürnberg

Tag der Verteidigung:

25.03.2025

# ADAPTIVE AND ENERGY-EFFICIENT MANAGEMENT FOR HETEROGENEOUS MULTI-CORE ARCHITECTURES

ROBERT KHASANOV

June, 2025

Robert Khasanov: *Adaptive and Energy-Efficient Management for Heterogeneous Multi-Core Architectures,* Dissertation © 2025

#### ABSTRACT

The evolution of processor architectures has seen a significant shift over the past few decades, driven by increasing application demands. Historically, general-purpose computing systems focused on increasing clock speeds and later transitioned to multi-core architectures. At the same time, embedded systems focused on energy-efficient designs and shifted to heterogeneous architectures to handle increasingly complex applications. Over time, the boundaries between embedded and general-purpose systems began to blur: embedded systems integrated multitasking operating systems and started handling more dynamic workloads, while general-purpose systems have adopted energy-efficient principles. This convergence led to the emergence of Heterogeneous Multi-core Architectures (HMAs), which combines cores with different performance-energy characteristics but a shared Instruction Set Architecture (ISA), enhancing energy efficiency while allowing workloads to migrate between core types. Initially introduced in embedded systems, HMAs have since expanded to powerful desktop and server platforms, further blurring the boundaries between the two domains.

Dynamic and unpredictable workloads, now prevalent in both domains, demand flexibility and *adaptivity* in *resource management* and *application execution*. HMAs add complexity to these challenges: resource managers must account for heterogeneous cores when allocating resources, while applications must adapt not only to dynamically changing allocations but also to the heterogeneity of the assigned cores.

This thesis proposes a series of solutions to address these adaptivity challenges. At the resource management level, it builds upon Hybrid Application Mapping (HAM) methodologies, introducing novel algorithms for generating spatio-temporal mappings and leveraging domain-specific knowledge to enhance adaptivity in real-time systems. At the application level, this thesis introduces an extension to Kahn Process Networks (KPNs), improving adaptivity in dynamic and heterogeneous environments. Finally, it asserts that fully utilizing HMAs requires coordinated adaptivity between these two levels. This coordination is demonstrated with HARP, a novel resource management framework, which can also efficiently manage unforeseen applications, thereby extending its applicability to desktop and server systems. By addressing both embedded systems and general-purpose platforms featuring HMAs, this thesis optimizes the utilization of these architectures and improves energy efficiency across domains.

#### PUBLICATIONS

Several ideas, figures and arguments that are presented in this dissertation have been published in prior works. The following lists all the publications cited in this thesis that I co-authored:

- Till Smejkal, Robert Khasanov, Jeronimo Castrillon, and Hermann Härtig. E-Mapper: Energy-Efficient Resource Allocation for Traditional Operating Systems on Heterogeneous Processors. June 2024. arXiv: 2406.18980 [cs.05].

- Robert Khasanov, Marc Dietrich, and Jeronimo Castrillon. "Flexible Spatio-Temporal Energy-Efficient Runtime Management." In: 2024 29th Asia and South Pacific Design Automation Conference (ASP-DAC). Jan. 2024, pp. 777–784. DOI: 10.1109/ASP -DAC58780.2024.10473885.

- [3] Robert Khasanov, Julian Robledo, Christian Menard, Andrés Goens, and Jeronimo Castrillon. "Domain-specific Hybrid Mapping for Energy-efficient Baseband Processing in Wireless Networks." In: ACM Trans. Embed. Comput. Syst. 20.5s (Oct. 2021). ISSN: 1539-9087. DOI: 10.1145/3476991.

- [4] Christian Menard, Andrés Goens, Gerald Hempel, Robert Khasanov, Julian Robledo, Felix Teweleitt, and Jeronimo Castrillon. "Mocasin—Rapid Prototyping of Rapid Prototyping Tools: A Framework for Exploring New Approaches in Mapping Software to Heterogeneous Multi-cores." In: Proceedings of the 2021 Drone Systems Engineering and Rapid Simulation and Performance Evaluation: Methods and Tools Proceedings. DroneSE and RAPIDO '21. Budapest, Hungary: Association for Computing Machinery, Jan. 2021, pp. 66–73. ISBN: 9781450389525. DOI: 10.1145/3444950.3447285.

- [5] Robert Khasanov and Jeronimo Castrillon. "Energy-efficient Runtime Resource Management for Adaptable Multi-application Mapping." In: 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE). Mar. 2020, pp. 909–914. DOI: 10. 23919/DATE48585.2020.9116381.

- [6] Robert Khasanov, Andrés Goens, and Jeronimo Castrillon. "Implicit Data-Parallelism in Kahn Process Networks: Bridging the MacQueen Gap." In: Proceedings of the 9th Workshop and 7th Workshop on Parallel Programming and RunTime Management Techniques for Manycore Architectures and Design Tools and Architectures for Multicore Embedded Computing Platforms. PARMA-DITAM '18. Manchester, United Kingdom: Association for Com-

puting Machinery, Jan. 2018, pp. 20–25. ISBN: 978-1-4503-6444-7. DOI: 10.1145/3183767.3183790.

[7] Andrés Goens, Robert Khasanov, Jeronimo Castrillon, Marcus Hähnel, Till Smejkal, and Hermann Härtig. "TETRiS: a Multi-Application Run-Time System for Predictable Execution of Static Mappings." In: *Proceedings of the 20th International Workshop on Software and Compilers for Embedded Systems*. SCOPES '17. Sankt Goar, Germany: Association for Computing Machinery, 2017, pp. 11–20. ISBN: 9781450350396. DOI: 10.1145/3078659. 3078663.

The following publications are co-authored by me but not cited in this thesis:

- Shaokai Lin, Tassilo Tanneberger, Jiahong Bi, Guangyu Feng, Yimo Xu, Julian Robledo, Robert Khasanov, and Jeronimo Castrillon. "Navigating Time and Energy Trade-Offs in Reactive Heterogeneous Systems." In: *IEEE Embedded Systems Letters* (2024), pp. 1–1. DOI: 10.1109/LES.2024.3469278.

- [2] Markus Hahnel, Frehiwot Melak Arega, Waltenegus Dargie, Robert Khasanov, and Jeronimo Castrillon. "Application interference analysis: Towards energy-efficient workload management on heterogeneous micro-server architectures." In: 2017 IEEE Conference on Computer Communications Workshops (INFO-COM WKSHPS). 2017, pp. 432–437. DOI: 10.1109/INFCOMW. 2017.8116415.

- [3] Andres Goens, Robert Khasanov, Jeronimo Castrillon, Simon Polstra, and Andy Pimentel. "Why Comparing System-Level MPSoC Mapping Approaches is Difficult: A Case Study." In: 2016 IEEE 10th International Symposium on Embedded Multicore-/Many-core Systems-on-Chip (MCSoC). 2016, pp. 281–288. DOI: 10.1109/MCSoC.2016.48.

It takes a village to raise a child. — African proverb

#### ACKNOWLEDGMENTS

First and foremost, I want to express my sincere gratitude to my supervisor Prof. Jeronimo Castrillon for his continuous support, insightful guidance, and encouragement throughout my Ph.D. journey. His mentorship helped me grow as a confident and independent researcher, and also taught me to focus on important problems that matter from a research and practical perspective. I am also grateful for his timely feedback, even on weekends, and for building a friendly and supportive atmosphere within the group.

Speaking of friendly atmosphere in the group, I owe a huge thank you to my current and former colleagues: Justus Adam, Jiahong Bi, Hasna Bouraoui, Alexander Brauckmann, Sebastian Ertel, Mees Frensel, Andrés Goens, Fazal Hameed, Gerald Hempel, Hamid Farzaneh, Clément Fournier, Karl Friebel, Sven Karol, Asif Khan, Nesrine Khouzami, Steffen Köhler, Guilherme Korol, Galina Kozyreva, João Paulo Cardoso de Lima, Christian Menard, Norman Rink, Julian Robledo, Lars Schütze, Anderson Faustino da Silva, and Felix Suchert. You all made this time unforgettable, from the insightful discussions to the fun team activities. And thank you for (patiently!) putting up with my reminders to give a tech talk. A special thanks to Conny Okuma, whose responsiveness and support with administrative matters were invaluable, as well as for urging us to participate in running trainings. I also enjoyed sharing skiing and snowboarding trips with you and other colleagues.

I also want to thank everyone who worked with me as a student. This includes Marc Dietrich, Hannes Frank, Karl Friebel, Dylan Gageot, Fabius Mayer-Uhma, and Tianrui Zheng. Working with you allowed me to explore side projects, many of which influenced my research vision. It was also rewarding to witness your efforts and growth as you overcame challenges in your work. I am happy to see some of you already becoming successful engineers and researchers, and in one case, a colleague.

During my work, I have closely collaborated with the Chair of Operating Systems. First and foremost, I am honored to have Prof. Hermann Härtig as my second advisor, and I am grateful to him for his valuable feedback on my status talk and the papers we worked on together with members of his chair. This collaboration included Marcus Hähnel and Till Smejkal, with whom I worked on the TETRiS project. Over time, this project evolved into HARP, presented in this thesis, on which I collaborated intensively with Till Smejkal. Till, it was an amazing collaboration. Looking back at how this project evolved over time, especially in the last two years, it feels like we wrote multiple different papers.

I also want to thank the rest of my collaborators that I have not mentioned personally so far. While not all of these projects became part of this thesis, they influenced my broader research vision. Thanks to Markus Hähnel and Frehiwot Melak Arega for the insightful work on the application interference analysis. I thank Arka Maity, Nishant Budhev and Tulika Mitra for sharing their LTE traces with our chair. Thanks to Tung Doan for collaborating on the adaptive self-driving car control project, which resulted in a well-received demonstration. I thank also Shaokai Lin for inviting me to contribute to the work of integrating the Lingua Franca and Mocasin projects.

During my time at the chair, I had an opportunity to work with several tools and frameworks that were generously provided to our group. This includes the Silexica Tool Suite, which was valuable at the beginning of my research. My earliest prototype of Adaptive Process Networks was implemented within this framework.

The work conducted in this thesis would not have been possible without funding. My Ph.D. studies were initially funded by the German Research Foundation (DFG) in the Collaborative Research Center 912 "Highly Adaptive Energy-Efficient Computing" (HAEC), and later by Federal Ministry of Education and Research of Germany (BMBF) within the programme of "Souverän. Digital. Vernetzt." (6G-life). Both projects also provided an excellent environment for collaboration, which was invaluable throughout my Ph.D. studies.

Finally, and most importantly, I want to thank my friends and family, who constantly reminded me about other aspects of life beyond work. Here in Dresden, I have found friends who have accompanied me through these nine years — thank you for making this one of the best times of my life. To my friends from Russia, whom I met during my time at MIPT and even earlier during my school years, I am grateful that we maintain our friendships. Even though we are spread around the world, I am glad that we occasionally have the chance to visit each other.

I would not have been able to write this thesis without the tremendous support of my family. My parents, grandparents, little brother, aunt, and cousins — it is difficult to express how thankful I am for your constant encouragement and for always being there for me, even from afar. To my mother, I am especially grateful for nurturing my curiosity and giving me the freedom to pursue my passions.

Robert Khasanov, December 2024

# CONTENTS

| 1 | Introduction                                 |                                                     |    |  |  |  |  |

|---|----------------------------------------------|-----------------------------------------------------|----|--|--|--|--|

|   | 1.1                                          | 1.1 Heterogeneous Multi-Core Architectures          |    |  |  |  |  |

|   | 1.2                                          | Need for Adaptivity                                 | 4  |  |  |  |  |

|   |                                              | 1.2.1 Adaptivity at the Resource Management Level . | 5  |  |  |  |  |

|   |                                              | 1.2.2 Adaptivity at the Application Level           | 6  |  |  |  |  |

|   | 1.3                                          | Contributions of This Thesis                        | 7  |  |  |  |  |

|   | 1.4 Synopsis and Outline                     |                                                     |    |  |  |  |  |

| 2 | Foundations of Application Mapping onto HMAs |                                                     |    |  |  |  |  |

|   | 2.1 Preliminaries                            |                                                     |    |  |  |  |  |

|   |                                              | 2.1.1 Mapping, Scheduling, and Spatio-Temporal Map- |    |  |  |  |  |

|   |                                              | ping                                                | 11 |  |  |  |  |

|   |                                              | 2.1.2 Performance and Energy Estimation             | 14 |  |  |  |  |

|   |                                              | 2.1.3 Static and Dynamic Power Consumption          | 15 |  |  |  |  |

|   |                                              | 2.1.4 Notation                                      | 16 |  |  |  |  |

|   | 2.2                                          | System Model                                        | 16 |  |  |  |  |

|   |                                              | 2.2.1 Architecture                                  | 17 |  |  |  |  |

|   |                                              | 2.2.2 Application                                   | 18 |  |  |  |  |

|   |                                              | 2.2.3 Mapping                                       | 19 |  |  |  |  |

|   | 2.3                                          | Mapping of Dataflow Applications                    | 19 |  |  |  |  |

|   |                                              | 2.3.1 Dataflow Models of Computation                | 20 |  |  |  |  |

|   |                                              | 2.3.2 Design-time and Runtime Mapping Approaches    | 22 |  |  |  |  |

|   |                                              | 2.3.3 Trace-Based Simulation                        | 23 |  |  |  |  |

|   | 2.4                                          | Hybrid Application Mapping                          | 25 |  |  |  |  |

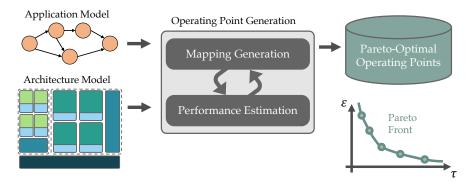

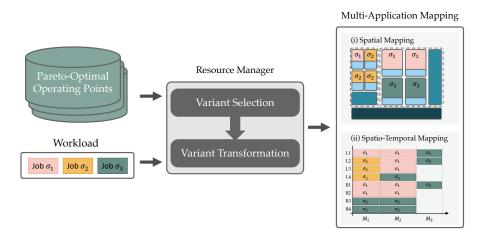

|   |                                              | 2.4.1 Pareto-Optimal Operating Points               | 27 |  |  |  |  |

|   |                                              | 2.4.2 Spatial Mapping Optimization                  | 30 |  |  |  |  |

|   |                                              | 2.4.3 Spatio-Temporal Mapping Optimization          | 32 |  |  |  |  |

|   |                                              | 2.4.4 Addressing Adaptivity Challenges              | 34 |  |  |  |  |

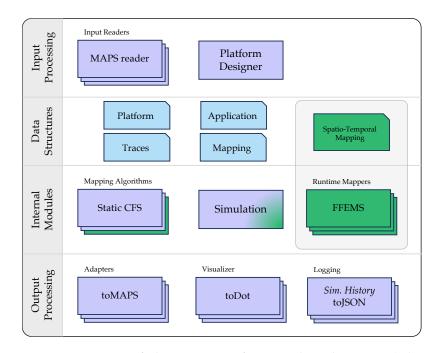

|   | 2.5                                          | Mocasin Framework                                   | 35 |  |  |  |  |

|   |                                              | 2.5.1 Overview of Mocasin                           | 35 |  |  |  |  |

|   |                                              | 2.5.2 Contributions to Mocasin                      | 37 |  |  |  |  |

|   | 2.6                                          | Synopsis                                            | 37 |  |  |  |  |

| 3 | Related Work 3                               |                                                     |    |  |  |  |  |

|   | 3.1                                          | Design-Time Application Mapping                     |    |  |  |  |  |

|   | 3.2                                          | Runtime Application Mapping                         | 40 |  |  |  |  |

|   |                                              | 3.2.1 Runtime Mapping of Embedded Software          | 40 |  |  |  |  |

|   |                                              | 3.2.2 Runtime Mapping within OS Schedulers          | 42 |  |  |  |  |

|   | 3.3                                          | Hybrid Application Mapping                          | 43 |  |  |  |  |

|   | 3.4 Application Adaptivity                   |                                                     |    |  |  |  |  |

| 4 | Efficient Spatio-Temporal Mapping Generation |                                                     |    |  |  |  |  |

|   | 4.1                                          | Motivational Example                                |    |  |  |  |  |

|   | 4.2                                          | Spatio-Temporal Mapping Strategies                  |    |  |  |  |  |

|   | 4.3 Fixed-Point Spatio-Temporal Mapping      |                                                     |    |  |  |  |  |

|   |            | 4.3.1                      | MMKP-based Algorithm                             | 52         |  |  |

|---|------------|----------------------------|--------------------------------------------------|------------|--|--|

|   |            | 4.3.2                      | Evaluation                                       | 56         |  |  |

|   | 4.4        | Flexib                     | le Spatio-Temporal Mapping                       | 60         |  |  |

|   |            | 4.4.1                      | STEM: Spatio-Temporal Evolutionary Mapping       | 60         |  |  |

|   |            | 4.4.2                      | FFEMS: Fast Flexible Energy-Minimizing Sched-    |            |  |  |

|   |            |                            | uler                                             | 64         |  |  |

|   |            | 4.4.3                      | Evaluation                                       | 67         |  |  |

|   | 4.5        |                            | sis                                              | 74         |  |  |

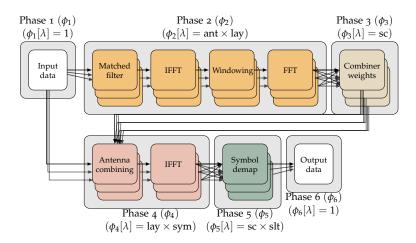

| 5 |            | 5 1                        | ecific Hybrid Mapping for Baseband Processing    | 75         |  |  |

| 2 | 5.1        |                            | aches to Baseband Processing                     | 76         |  |  |

|   | 5.2        | 11                         | and Processing Architecture and Parameterization | ,<br>78    |  |  |

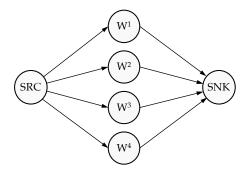

|   | 5·3        |                            | Graph with Phase-Sequential Structure            | ,<br>79    |  |  |

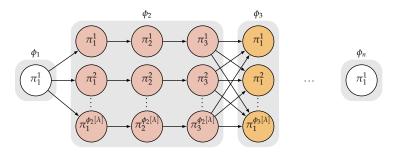

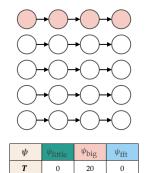

|   | 5·4        |                            | nt Mapping Algorithm for Phased Task Graphs .    | 80         |  |  |

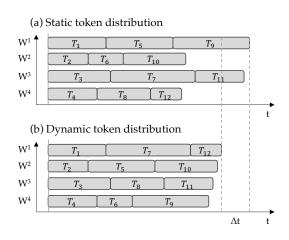

|   | 5.5        |                            | -Temporal Mapping Reusing Previous Solutions     | 84         |  |  |

|   | 5.6        | -                          | ation                                            | 86         |  |  |

|   | 510        | 5.6.1                      | Platform Setup                                   | 86         |  |  |

|   |            | 2                          | Workload Model                                   | 87         |  |  |

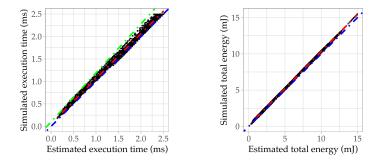

|   |            | <i>J</i>                   | Generation and Estimation of Operating Points    | 88         |  |  |

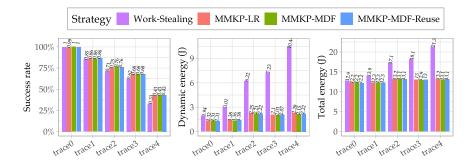

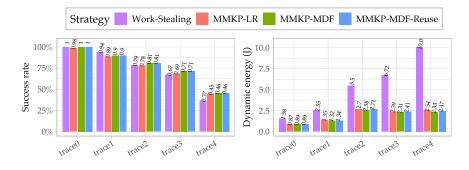

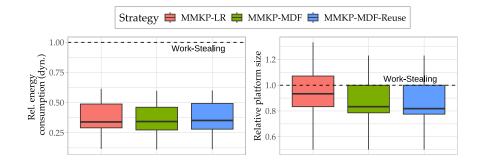

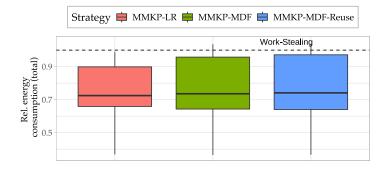

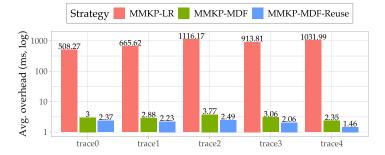

|   |            | 5.6.4                      | Energy-Efficient Runtime Mapping                 | 91         |  |  |

|   | 5.7        | J .                        | sis                                              | 91<br>95   |  |  |

| 6 |            | <b>5</b> 1                 | Kahn Process Networks with Adaptivity            | 95<br>97   |  |  |

| 0 | 6.1        | 0                          | tions of KPNs: A Motivational Example            | 97<br>98   |  |  |

|   | 6.2        |                            | ive Process Network                              | 90<br>100  |  |  |

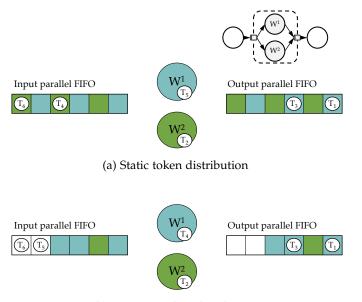

|   | 0.2        | 6.2.1                      | Parallel Regions                                 | 100        |  |  |

|   |            | 6.2.2                      | Parallel Channels and Workload Distribution      | 100        |  |  |

|   |            | 6.2.3                      | Malleability                                     | 102        |  |  |

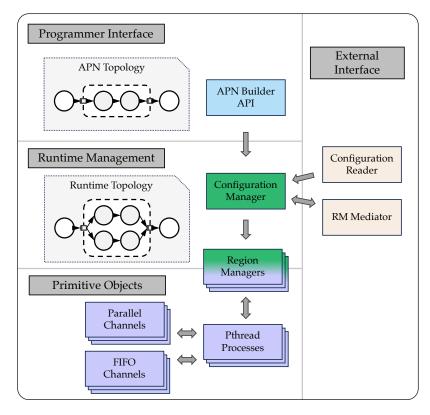

|   | 6.3        | 5                          | nic Process Manager (DPM) Library                | 104<br>105 |  |  |

|   | 0.3        | 6.3.1                      | Programmer Interface                             | 105        |  |  |

|   |            | 6.3.2                      | Runtime Topology                                 | 100        |  |  |

|   |            | 6.3.3                      |                                                  | 100        |  |  |

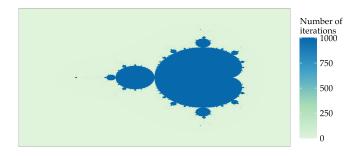

|   | 6.4        | 00                         |                                                  | 110        |  |  |

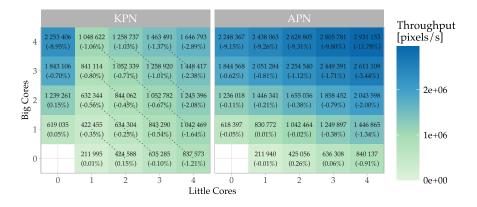

|   | 0.4        | 6.4.1                      | Experimental Setup                               |            |  |  |

|   |            | 6.4.1<br>6.4.2             | Performance Scalability with Parallelization     | 110<br>111 |  |  |

|   |            | 6.4.3                      | Runtime Adaptivity                               |            |  |  |

|   | 6.5        |                            | sis                                              | 112<br>113 |  |  |

| - |            |                            | ng Adaptivity in General-Purpose Environments    | -          |  |  |

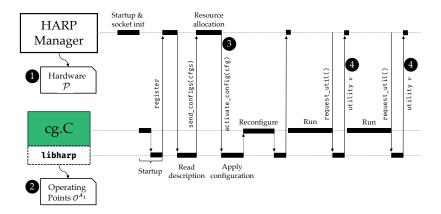

| 7 | 7.1        |                            | for Two-Way Communication                        | 115<br>116 |  |  |

|   | 7.1<br>7.2 | Adapting HAM Methodologies |                                                  |            |  |  |

|   |            | -                          | <sup>9</sup> Design                              |            |  |  |

|   | 7.3        |                            | Application Support via Libharp                  | 119        |  |  |

|   |            | 7.3.1                      | Resource Allocation                              | 120        |  |  |

|   | -          | 7.3.2<br>Puptir            |                                                  | 123        |  |  |

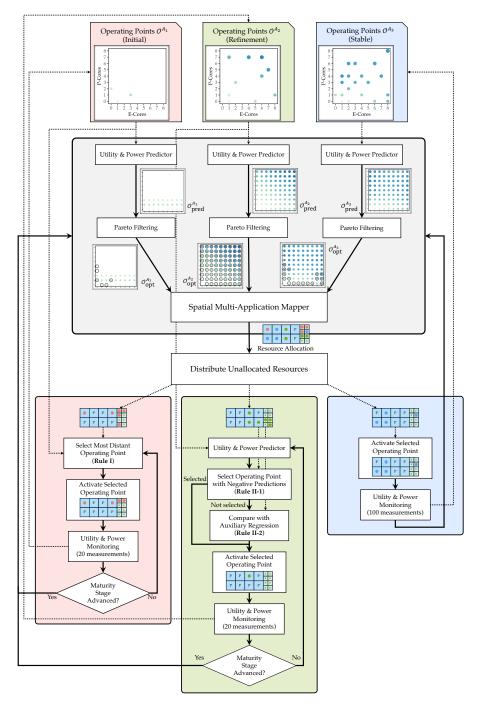

|   | 7.4        |                            | ne Exploration of Operating Points               | 125<br>126 |  |  |

|   |            | 7.4.1                      | Runtime Performance and Power Monitoring .       | 126        |  |  |

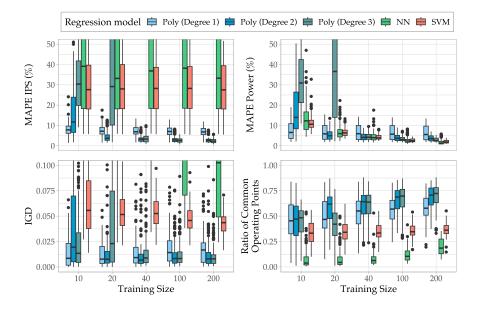

|   |            | 7.4.2                      | Selection of the Regression Model                | 126        |  |  |

|   |            | 7.4.3<br>Evolut            | Runtime Exploration Algorithm                    | 128        |  |  |

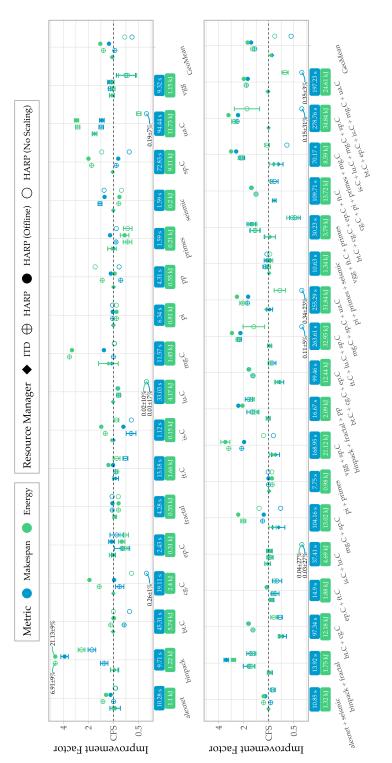

|   | 7.5        | Evalua                     | ation                                            | 130        |  |  |

|   | 7.5.1                                                    | Experimental Setup                   | 131 |  |  |  |  |

|---|----------------------------------------------------------|--------------------------------------|-----|--|--|--|--|

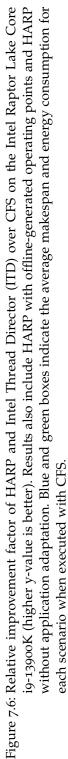

|   | 7.5.2                                                    | Intel Raptor Lake Evaluation         | 133 |  |  |  |  |

|   | 7.5.3                                                    | Odroid-XU <sub>3</sub> -E Evaluation | 135 |  |  |  |  |

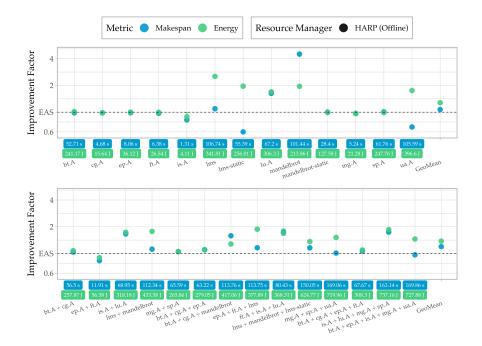

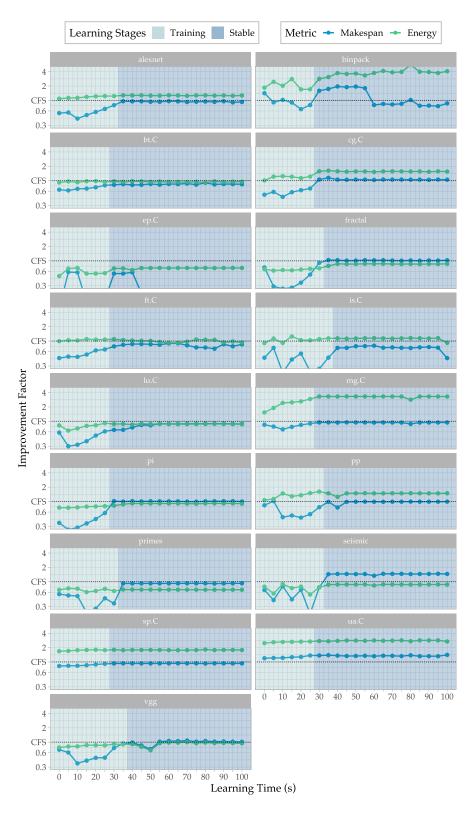

|   | 7.5.4                                                    | Evaluation of the Learning Process   | 137 |  |  |  |  |

|   | 7.5.5                                                    | Performance Overhead of HARP         | 140 |  |  |  |  |

|   | 7.6 Synop                                                | osis                                 | 141 |  |  |  |  |

| 8 | Conclusions and Outlook                                  |                                      |     |  |  |  |  |

|   |                                                          |                                      |     |  |  |  |  |

|   | Glossary                                                 |                                      |     |  |  |  |  |

|   | List of Figures                                          |                                      |     |  |  |  |  |

|   | List of Tables<br>List of Algorithms<br>List of Listings |                                      |     |  |  |  |  |

|   |                                                          |                                      |     |  |  |  |  |

|   |                                                          |                                      |     |  |  |  |  |

|   | Bibliograph                                              | Ŋ                                    | 163 |  |  |  |  |

|   |                                                          |                                      |     |  |  |  |  |

#### INTRODUCTION

The evolution of processor architectures has seen a significant shift over the past few decades, driven by the increasing demands of applications. In general-purpose computing, early performance improvements were primarily driven by *Moore's Law* [134], which predicted that the number of transistors on a chip would doubles every 18–24 months. As transistor sizes shrank, clock frequencies also doubled over the same period, since the processing speed is inversely related to the distance between transistors. This trend was further aided by *Dennard Scaling* [55], which maintained constant power density [59].

However, starting at 65 nm process technology and below, leakage power began to rise exponentially, breaking Dennard Scaling and preventing further increases in clock frequency. To continue performance scaling, computer systems transitioned toward *multi-core architectures*, where multiple processing elements are integrated on a single chip [67]. In these systems, individual core frequencies and complexity were kept constant or even reduced to accommodate for the breakdown of Dennard scaling, and performance improvement were instead achieved through *Thread-Level Parallelism* (TLP) [131].

After certain point, core scaling hit the power budget: additional cores could be added, but they often had to be switched off or significantly underclocked to satisfy the *Thermal Design Power* (TDP) constraints. This phenomenon has been termed as *Dark Silicon* [59]. In response, processor designs began transitioning to *heterogeneous architectures*, where only the cores best suited to the application are activated, enabling faster and energy-efficient computing [131].

The shift toward heterogeneous architectures was seen much earlier in the embedded systems domain. In embedded systems, the focus was traditionally on energy efficiency, real-time constraints, and cost-effectiveness rather than solely increasing performance [125]. Historically, embedded software consisted of simple routines within a single control loop, that were often programmed in assembly. However, modern embedded devices run much more complex applications such as baseband and multimedia processing, including video conferencing and voice recognition [19, 95, 213]. This shift necessitated the adoption of multi-core architectures to handle increased computational demands while maintaining low power consumption and meeting real-time performance requirements [18].

To achieve energy efficiency and meet application needs, embedded systems have traditionally employed heterogeneous architectures that integrate different types of processing units, such as Central Processing

#### 2 INTRODUCTION

Units (CPUs), Digital Signal Processors (DSPs), Application-Specific Instruction-Set Processors (ASIPs), and hardware accelerators (e.g., FPGAs) [84, 125]. While this approach allows for specialized and energy-efficient designs, it also presents challenges due to differing Instruction Set Architectures (ISAs), making software development more complex and limiting task migration across processing units.

Over time, the boundary between embedded and general-purpose computing systems began to blur. Embedded systems have adopted functionalities commonly associated with personal computers, such as multitasking operating systems in mobile devices [82], and have started handling more dynamic workloads [22]. Conversely, generalpurpose computing systems, facing the limitations of the TDP constraints, began adopting energy-efficient design principles traditionally associated with embedded systems [14]. This convergence has led to the emergence of Heterogeneous Multi-core Architectures (HMAs), which combine different core types within a single processor [8, 106].

These core types share the same ISA but differ in microarchitecture, offering different performance-energy trade-offs while maintaining software compatibility. This design enhances flexibility and allows for the dynamic resource allocation across core types [72]. Initially introduced in the embedded domain [8, 72], HMAs have since expanded to general-purpose computing [7, 86, 118], offering opportunities to optimize performance and energy-efficiency across domains.

However, this new form of heterogeneity also brings new challenges in resource allocation and application design [103]. Dynamic and unpredictable workloads, now prevalent in both embedded and general-purpose domains, demand flexibility and *adaptivity* at both *resource management* and *application* levels. Resource managers must account for the differing characteristics of heterogeneous cores when scheduling and distributing workloads, while applications must adapt not only to dynamically changing resource allocations but also to the heterogeneity of the assigned cores. Traditional methods may not be well-suited for fully leveraging the capabilities of these heterogeneous systems [163], requiring new strategies for scheduling, workload distribution, and application design.

This thesis explores the adaptivity challenges posed by HMAs and proposes comprehensive solutions at both the resource management and application levels. By addressing these challenges, the work aims to enhance performance and energy efficiency of modern processors, spanning embedded to general-purpose computing systems.

#### 1.1 HETEROGENEOUS MULTI-CORE ARCHITECTURES

*Heterogeneous Multi-core Architectures* (HMAs) were initially introduced in mobile and embedded devices, with Arm's big.LITTLE architecture [8], which features two core clusters — one with high-performance

3

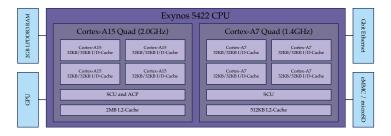

Figure 1.1: Samsung Exynos 5422 CPU implementing the Arm's big.LITTLE architecture with two core clusters: a four-core Cortex-A15 (big) cluster and a four-core Cortex-A7 (LITTLE) cluster.

cores and one with energy-efficient cores (see Figure 1.1). This design later evolved into Arm's DynamIQ, which supports more flexible core configurations and more core types [9, 203]. Since then, HMAs have been adopted in desktop systems, beginning with Apple's M1 chip [7], and followed by incorporation into powerful x86 processors for desktops and servers, such as Intel's Alder Lake and Raptor Lake [86], as well as AMD's Phoenix 2 [29, 118] and Strix Point [79] processors. Most of these processors feature two types of cores, but different vendors use various names for these core types: Arm refers to them as "big" and "LITTLE" cores, while Intel labels them as "P-cores" and "E-cores".

The performance-energy differences between core types arise from their microarchitectures. Energy-efficient cores typically have simpler designs with shorter pipelines, in-order execution, and smaller caches, which contribute to lower power consumption but also lower single-thread performance. On the other hand, high-performance cores often feature deeper pipelines, out-of-order execution, larger caches, and other features like Simultaneous Multithreading (SMT), enabling higher performance but at the cost of increased power consumption.

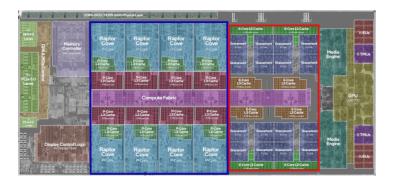

This difference is also reflected in the die area. As illustrated in Figure 1.2, high-performance P-cores on modern Intel Raptor Lake processors occupy significantly more space on the die than energy-

Figure 1.2: Labeled die shot of an Intel Raptor Lake Core i9-13900K. P-cores are located in the blue rectangle, and E-cores in the red one. Original die shot from [89].

#### 4 INTRODUCTION

efficient E-cores, even though the number of E-cores is larger than that of P-cores. The larger area required by P-cores also results in higher static power consumption.

Despite these microarchitectural differences, both core types share the same ISA, ensuring compatibility at the software level. This allows the Operating System (OS) to schedule and migrate tasks seamlessly across them, enabling dynamic trade-offs between performance and energy consumption. This flexibility allows systems to optimize performance and energy efficiency based on current workloads and requirements. For instance, compute-intensive tasks can be assigned to high-performance cores, while background and less demanding tasks can run on energy-efficient cores, reducing power consumption without compromising user experience.

However, HMAs also introduce new challenges for efficient application execution and resource allocation. Traditional execution models and resource allocation strategies may not be sufficient to fully leverage the capabilities of HMAs. This necessitates new approaches to application design, scheduling, and resource management that can exploit the advantages of heterogeneous cores.

In the following section, we explore the specific adaptivity challenges posed by modern HMAs and highlight the need for adaptive solutions that can fully leverage their potential.

#### 1.2 NEED FOR ADAPTIVITY

As already mentioned, modern systems, both embedded and generalpurpose, often execute dynamic and unpredictable workloads. Applications may start and stop unpredictably, triggered either by user interaction in general-purpose systems or by external sensors and events in embedded systems. Moreover, applications exhibit varied behaviors: some are compute-intensive and others are memory-intensive. Workloads also vary in priority, ranging from high-priority tasks to less critical background processes. The heterogeneity of input data also contributes to the unpredictability of resource demands.

At the same time, systems must ensure performance requirements are met. Embedded applications often have strict deadlines, while non-real-time applications in general-purpose systems, though not bound to explicit deadlines, must maintain acceptable performance to meet user expectations. Energy efficiency has also become a critical consideration across both domains.

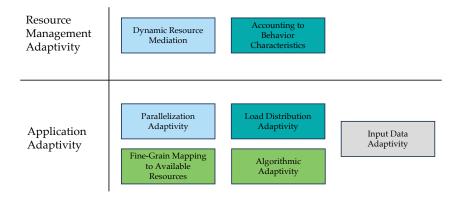

To meet these demands, systems must balance energy efficiency and performance while being flexible and *adaptive* to dynamic workloads. These adaptivity requirements can be categorized at two levels: the *resource management level* and the *application level* (see Figure 1.3).

Figure 1.3: Some adaptivity challenges at the resource management and application levels brought by modern processors.

#### 1.2.1 Adaptivity at the Resource Management Level

Since the introduction of multi-core systems, the system has to perform the resource management tasks: *space-sharing*, allocating tasks across processor cores. Traditionally, resource management was integrated within OS schedulers, which were previously focused on dividing processor time among tasks through *time-sharing*.

Resource managers must dynamically consider current workloads and system conditions when making decisions. This dynamism is necessary because systems often run multiple applications concurrently, with applications starting and stopping at any time, leading to fluctuating resource demands and necessitating dynamic reallocation of processor cores. The Resource Manager (RM) must adaptively assign cores to applications, ensuring efficient utilization of resources and maintaining system performance metrics such as overall throughput, fairness, or for real-time applications, meeting deadlines.

The introduction of HMAs adds complexity to resource allocation due to the varying performance-energy characteristics of different core types. The RM now also needs to determine which core type to allocate to each running task. This decision can be guided by different strategies, ranging from checking which of the applications are running in the background or actively used by a user [52] to analyzing applications' live behavior characteristics. For example, for memory- and I/O-bound applications, the performance gap between the core types may be minimal, making it more energy-efficient to run these applications on energy-efficient cores, while compute-intensive applications are located to high-performance cores.

Resource managers must make informed decisions about assigning tasks to appropriate core types. These decisions should optimize performance and energy efficiency while adapting to the dynamic workload, which requires consideration of the applications' characteristics and how they interact with different core types.

#### 1.2.2 Adaptivity at the Application Level

Since the RM changes the resource allocation dynamically, each application may have access to different processor resources at different times. However, many applications are not designed to dynamically adjust their resource usage, whether by modifying their parallelization degree or accounting for heterogeneity in processor cores. Moreover, applications are often *unaware* of the specific processors on which they are executed, as the RM decisions are not explicitly communicated to them. To fully utilize processor resources, applications must adapt to the processor cores allocated by the RM.

Parallel applications typically spawn multiple threads to parallelize execution, such as data-parallel applications that distribute data processing among worker threads. Ideally, the number of threads should align with the available processor cores. This alignment helps to prevent inefficiencies such as the contention among threads for the same core. To handle the dynamic availability of processor cores, applications must be capable of adjusting their parallelization degree at runtime, scaling down their resource usage when cores are needed by other applications, and scaling up when additional resources become available.

Heterogeneous processors introduce additional challenges for applications, requiring adaptivity in workload distribution, application topology, or even algorithms. For instance, if parallel threads are distributed across both high-performance and energy-efficient cores, the slower threads on energy-efficient cores can create a bottleneck, causing load imbalance and underutilization of high-performance cores, thereby reducing overall performance.

In some cases, these adaptivity challenges can be addressed agnostically, without requiring the application to know which threads are assigned to which core types. For example, workload distribution can be dynamically managed using techniques like work-stealing in shared task pools (e.g., in OpenMP [160]). However, other solutions may require explicit awareness of the processor cores available to the application. This includes the ability to adjust the parallelization degree, reconfiguring application topology, or selecting algorithms optimized for specific core types [155, 156, 166].

Apart from adapting to available resources, applications may also adapt to their input data, which contributes to the unpredictability of resource demands. Input data can significantly influence an application's behavior [153, 165, 184]. For example, a WLAN application may switch between *send* and *receive* modes depending on input, altering the active component within the application. Internally, applications are often designed to adapt to input data, but these adaptations can result in varying execution characteristics and the resource demands. Thus, to fully utilize processor resources, there is a need for a communication mechanism to ensure applications are aware of the available processor cores. Conversely, RM should also be aware of the dynamic characteristics of applications, to make more informed resource allocation decisions.

#### **1.3 CONTRIBUTIONS OF THIS THESIS**

The adaptivity challenges posed by modern systems executing dynamic workloads require comprehensive and flexible solutions. While no single solution can fully address the adaptivity challenges of HMAs, this thesis proposes a series of approaches that enhance adaptivity in different scenarios, targeting both resource management and application behavior.

In the embedded domain, one promising state-of-the-art approach is *Hybrid Application Mapping* (HAM), which combines design-time application optimization with runtime resource management that dynamically adapts resource allocations based on current workloads. By integrating extensive offline analysis with online decision-making, HAM effectively addresses adaptivity challenges at the resource management level, such as dynamic resource mediation and accounting for unique application characteristics. Building upon the advantages of HAM, this thesis adopts it as a central methodology and enhances it to further improve adaptivity in resource management.

Beyond resource management, this thesis also examines adaptivity challenges at the application level, focusing on dataflow Models of Computation (MoCs). Furthermore, it proposes a coordinated mechanism that integrates adaptivity at both resource management and application levels.

The following subsections outline the key contributions of this thesis.

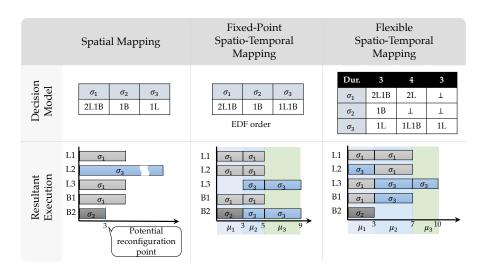

#### Spatio-Temporal Mapping in Real-Time Systems

This thesis tackles the challenge of efficiently mapping parallel applications in dynamic real-time environments where workloads may start sporadically. Each application is associated with a specific deadline, and the RM must ensure that all applications complete within their time constraints. State-of-the-art approaches typically generate only *spatial* mappings, which limit the overall performance and energy efficiency when responding to workload changes.

To overcome the limitations, this work proposes a novel resource management approach that generates *spatio-temporal* mappings. This decision model allows the resource manager to not only allocate resources spatially but also strategically postpone execution or adjust mappings at a later time, accounting for foreseen workload

#### 8 INTRODUCTION

changes. Two efficient algorithms are presented to generate energyefficient spatio-temporal mappings within milliseconds. Additionally, a memetic algorithm generating near-optimal solutions is proposed to validate and demonstrate the efficiency of the rapid heuristics.

#### Domain-Specific Hybrid Mapping for Baseband Processing

Baseband processing is a critical component of wireless communication systems. Modern standards demand high flexibility to handle heterogeneous and dynamic workloads. This thesis introduces a domain-specific HAM methodology tailored to the phased-sequential structure of baseband receiver applications, which comprise hundreds of tasks, with execution behavior depending on specific input data parameters.

The proposed approach leverages this phased structure to efficiently exploit processor heterogeneity. It presents a fast algorithm that generates optimal mappings accounting for the performance-energy characteristics of different cores. Additionally, a refined runtime resource allocation algorithm is proposed to utilize prior decisions, reducing runtime overhead, which is highly critical for low-latency baseband systems, and ensuring efficient resource utilization and improved performance.

#### Adaptive Process Networks

While the previous contributions focus on resource management through mapping selection, applications themselves must also adapt to dynamically allocated processor resources. This thesis examines application-level adaptivity within the Kahn Process Networks (KPNs), a MoC commonly used in embedded systems for streaming and dataflow applications due to their deterministic properties, expressiveness, and pipeline parallelism. Traditional KPNs, however, suffer from rigid application topology that limits their ability to adapt dynamically.

This thesis proposes *Adaptive Process Network* (APN), an implicit data-parallel extension to KPNs. This extension enables runtime replication of process subnetworks, allowing applications to adapt their topology dynamically. It also introduces parallel channels that dynamically distribute workloads among processes and merge results without compromising application determinism. The Dynamic Process Manager (DPM) library is developed to provide runtime support for APN applications and facilitate communication with the RM, enabling application awareness of the assigned resources.

#### Coordinated Adaptivity in General-Purpose Environments

To fully address adaptivity challenges, resource management and application-level adaptivity must be considered together and, therefore, coordinated. This thesis proposes HARP, a resource management framework integrated into Linux, which provides a unified resource allocation solution across various desktop system with heterogeneous processors.

HARP coordinates resource management across diverse application models through the Libharp library, which facilitates communication with the RM via a well-defined interface. This enables applications to internally adapt to allocated resources, such as adjusting their parallelization degree upon receiving the RM decisions. The Libharp library supports common application models like OpenMP and Intel TBB, while also allowing customization, for instance, for APN applications.

This contribution also expands the scope of the thesis to powerful desktop and server systems. This shift necessitates overcoming a key limitation of HAM: its reliance on offline analysis to generate Pareto-optimal application configurations. Since general-purpose systems may run unknown applications without pre-generated configurations, this thesis introduces a runtime algorithm that monitors application behavior to quickly identify optimal configurations.

In summary, this thesis advances the state-of-the-art by addressing adaptivity challenges at both the resource management and applications levels. The initial contributions of this thesis focused on embedded systems, where HMAs were first introduced. With HMAs now being adopted by major processor manufacturers for general-purpose systems, this work has evolved to address the adaptivity challenges in desktop and server environments as well.

#### A Note on Originality

The thesis primarily focuses on contributions that result from my own research. However, some of the presented work result from collaborative efforts. I believe that outstanding research often results from exchanging of ideas and collaboration. However, it can sometimes be challenging to attribute specific ideas or results to a single individual. To ensure transparency, I have made an effort throughout the thesis to clearly distinguish my contributions from those of collaborators. Additionally, I have indicated when the presented material appeared in joint publications. If in doubt, any idea or result that I have included here which has already been published elsewhere is also due to my coauthors.

#### 1.4 SYNOPSIS AND OUTLINE

This chapter has provided an overview of the evolution of modern processors, highlighting the transition from single-core designs to multi-core processors and, more recently, to heterogeneous multi-core architectures. It explored the opportunities and challenges brought by heterogeneous processors, emphasizing the need for adaptivity to fully exploit their capabilities. The chapter also provided an overview of this thesis's contributions, demonstrating how the identified adaptivity challenges are addressed at both the resource management and application levels, targeting both embedded and general-purpose computing systems.

The remainder of this thesis is organized as follows. The next chapter, Chapter 2, provides essential background information on application mapping and hybrid application mapping methodologies. The chapter also formalizes the system model and the optimization problems addressed in this thesis. Following this, Chapter 3 reviews the state-of-the-art, discussing relevant work in relation to the contributions of this thesis. The core contributions of the thesis are presented in Chapters 4 to 7, which cover spatio-temporal mapping for real-time systems, domain-specific hybrid mapping for baseband processing, the Adaptive Process Network (APN) application model, and a resource management approach coordinating adaptivity at both levels in general-purpose environments. Finally, Chapter 8 draws conclusions and outlines potential future research directions.

# FOUNDATIONS OF APPLICATION MAPPING ONTO HMAS

The previous chapter highlighted the need for adaptivity in modern heterogeneous multi-core processors and provided an intuitive overview of the Hybrid Application Mapping (HAM) methodology, emphasizing the existing gaps in fully utilizing Heterogeneous Multicore Architectures (HMAs). To provide a foundation for the subsequent chapters, this chapter introduces the key concepts, formal models, and tools relevant to our work, offering detailed information about application mapping to heterogeneous processors.

The chapter begins with Section 2.1, introducing basic terminology, discussing performance and energy estimation, and presenting the notation used throughout the thesis. Section 2.2 formalizes the system model. Section 2.3 explores the dataflow Model of Computation (MoC), including its mapping to heterogeneous multi-core architectures. Section 2.4 introduces the Hybrid Application Mapping (HAM) methodology, presenting its core principles and formalizing the optimization problems addressed in this thesis. Section 2.5 describes the MoCASIN framework, a rapid prototyping framework that is used in this research for modeling, simulating, and analyzing application mappings. The chapter ends with a summary in Section 2.6.

#### 2.1 PRELIMINARIES

Before introducing the formal problem definitions, this section introduces the fundamentals of mapping, scheduling, and spatio-temporal mapping, basic concepts of performance and energy estimation, static and dynamic power consumption, and the notation used throughout this thesis.

## 2.1.1 Mapping, Scheduling, and Spatio-Temporal Mapping

Efficient utilization of processing resources in multi-core and heterogeneous computing systems requires careful allocation of tasks to processor cores and the management of their execution over time. This involves two fundamental concepts: *mapping* and *scheduling* [42]. These terms recur throughout this thesis and are essential for understanding the proposed resource management strategies. Additionally, the concept of *spatio-temporal mapping* is a key aspect central to this work. Therefore, it is crucial to clearly define and distinguish them. *Mapping* is the process of assigning tasks to processor cores, determining which tasks run on which cores. This process can be performed either statically or dynamically. Static mapping determines task-tocore allocations at design time, remaining fixed during execution. It is common in systems with predictable workloads where timing guarantees are critical, such as real-time and embedded systems. In contrast, dynamic mapping assigns tasks to cores at runtime according to a *mapping policy*, allowing the system to adapt to changing workloads and resource availability.

*Scheduling* process decides on the order and timing of task execution on allocated cores, determining at which time instants tasks are to be run, managing the execution of multiple tasks that may compete for the same processing core. Similar to mapping, scheduling can also be static or dynamic. Static scheduling determines task order and timing at design time, providing precise control over task execution but lacking flexibility to adapt to dynamic workloads or varying system condition. Dynamic scheduling makes decisions about task execution at runtime based on *scheduling policies*, allowing the system to respond to unpredictable workloads.

Mapping and scheduling can either be coupled or decoupled. A decoupled mapper dispatches tasks to local schedulers on each processor core, which then decide on task execution. This approach might, for example, combine a fixed mapping strategy with a dynamic scheduling policy such as *First-Come*, *First-Served* (FCFS), where tasks are executed in the order they arrive at the scheduler [172]. In a coupled approach, both the *where* (mapping) and the *when* (scheduling) decisions are made jointly. An example is the *Earliest Finishing Time* (EFT) scheduling strategy, where tasks are assigned to processor cores in a way that minimizes their earliest finish time, making task-to-core assignment and scheduling order decisions simultaneously.

Alongside mapping and scheduling, the concept of spatio-temporal mapping play a central role in this thesis. *Spatio-temporal mapping* extends the mapping by introducing a temporal component and is defined as a sequence of *mapping segments*, where each segment specifies task-to-core allocation (the mapping) and the duration for which this mapping is active. In each mapping segment, multiple tasks may be assigned to the same core (as in conventional *spatial* mapping), but the specific order and timing of task execution within the segment are governed by scheduling, which may be governed by dynamic scheduling policy at runtime. While scheduling details the precise task timing and sequence (including context switches and preemptions), spatio-temporal mapping operates at a higher abstraction level, providing a time-dependent task allocation plan without specifying detailed scheduling decisions.

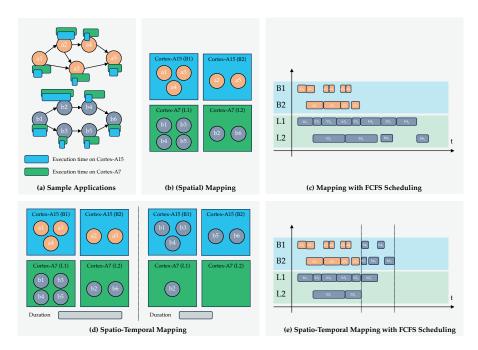

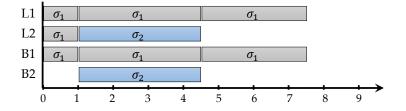

Figure 2.1 illustrates the concepts of mapping, scheduling, and spatio-temporal mapping. In this example, two applications, each rep-

Figure 2.1: Mapping, scheduling, and spatio-temporal mapping of two dataflow applications

resented as a Directed Acyclic Graph (DAG) and shown in Figure 2.1a, perform computations for two sample input data on HMA consisting of two Cortex-A15 (big) and two Cortex-A7 (LITTLE) cores. The colored bars attached to the nodes represent the execution time on each processor core, with communication costs ignored for simplicity.

Figure 2.1b shows spatial mapping, where tasks from the first application are mapped to the big cores, and tasks from the second application are mapped to the LITTLE cores. These tasks are then scheduled with the FCFS policy, shown in a *Gantt Chart* in Figure 2.1c, where time is plotted on the horizontal axis and the processor cores on the vertical axis.

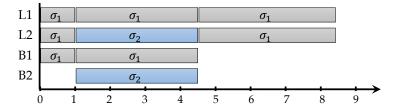

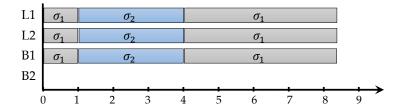

Figure 2.1d and Figure 2.1e illustrate an alternative approach utilizing spatio-temporal mapping, with two mapping segments shown in Figure 2.1d. The first mapping segment is the same as the spatial mapping, while the second reassigns some tasks from the second application to the big cores as they become available. Scheduling within each segment still follows the policy (as shown in Figure 2.1e), but the overall execution benefits from the dynamic adjustment of task mappings over time.

The resource management algorithms in this thesis focus primarily on mapping techniques — both spatial and spatio-temporal — without delving into the specifics of scheduling policies. During Design Space Exploration (DSE) and performance evaluation, a scheduling policy is assumed implicitly to assess the effectiveness of the mapping strategies. Therefore, *mapping* in this context refers broadly to both task assignment and the underlying scheduling policy governing task execution.

#### 2.1.2 Performance and Energy Estimation

Evaluating the effectiveness of application mappings (i.e., how applications perform under different mappings regarding performance and energy efficiency) on HMAs is essential to optimizing resource utilization, system performance, and energy efficiency. Common performance metrics include *execution time*, *throughput*, and application-specific *utility*, which may be defined based on the application's goals [101]. Energy metrics include *energy consumption*, *average power consumption*, and *peak power consumption*. Energy and performance metrics can be combined, resulting in metrics like the *Energy-Delay Product* (EDP), which considers both energy consumption and execution time [124, 144].

Various methods exist for assessing performance and energy metrics, depending on the application model, target architecture, available tools, and desired accuracy. Common evaluation methods include [42]:

- *Annotation-Based:* Estimates performance and energy by annotating code with expected values based on prior knowledge.

- *Source-Level Instrumentation*: Instruments source code to collect information about the execution of elementary operations, retrieving the costs of these operations from a table. While useful, this method may not accurately model complex operations, non-scalar architectures, or the effects of compiler optimizations [28].

- *Simulation-Based*: Uses simulators to model execution of the application on target hardware. Performance simulators estimate execution time by modeling processor behavior, while energy simulators use energy models to estimate energy consumption [31, 194].

- *Measurement-Based*: Measures actual performance and energy consumption by running applications on target hardware. This approach is potentially the most accurate but requires access to the real hardware. Energy measurements can be obtained using built-in sensors or external measurement tools, which vary in temporal and spatial granularity, accuracy, and cost [85].

This thesis relies primarily on measurement-based methods due to their accuracy. When possible, applications are executed on real hardware platforms equipped with energy measurement capabilities. Specifically, we employ Odroid-XU3<sup>1</sup> and Odroid-XU4 [78] boards; both feature Samsung Exynos 5422 CPUs (Figure 1.1), but only the

<sup>1</sup> Currently discontinued, https://www.hardkernel.com/shop/odroid-xu3

Odroid-XU<sub>3</sub> has onboard INA<sub>231</sub> energy sensors<sup>2</sup> to monitor the big and LITTLE cores, Graphics Processing Unit (GPU) and DRAM individually. For Odroid-XU<sub>4</sub>, we use the ZES Zimmer LMG<sub>450</sub> power meter, which measures the power consumption of the entire system at a sampling rate of 20 Sa/s [218].

For the Intel Raptor Lake system, energy data is collected using the *Running Average Power Limit* (RAPL) interface, which provides data with high temporal (as fine as 1 ms) and spatial (RAM, CPU per socket) granularity [54, 85]. The accuracy of RAPL for fine-grained energy measurements has been validated in several studies [51, 74, 75, 164, 179].

When direct measurement is not feasible — for instance, when evaluating a virtual target architecture — we utilize simulation-based methods. For KPN applications, we employ trace-based simulation using the *Mocasin* tool (Section 2.5) to estimate performance and energy consumption based on collected execution traces [42].

#### 2.1.3 Static and Dynamic Power Consumption

Processor power consumption consists of static and dynamic components:

$$P \coloneqq P_{\text{static}} + P_{\text{dynamic}} \tag{2.1}$$

• *Static Power Consumption*: Power consumed due to leakage currents even when the processor is idle.

$$P_{\text{static}} \coloneqq I_q \cdot V_{\text{dd}} \tag{2.2}$$

where  $I_q$  is leakage current and  $V_{dd}$  is supply voltage.

• *Dynamic Power Consumption*: Power consumed due to active computation and switching activities within the processor.

$$P_{\text{dynamic}} \coloneqq \gamma \cdot \hat{C}_{\text{eff}} \cdot V_{\text{dd}}^2 \cdot f_{\text{op}}$$

(2.3)

where  $\gamma \in [0,1]$  is average switching activity,  $\hat{C}_{\text{eff}}$  is effective capacitance, and  $f_{\text{op}}$  is operating frequency.

Distinguishing between static and dynamic power is important for evaluation the application's energy efficiency, especially in multiapplication scenarios, to avoid double-counting static energy when evaluating the total energy consumption.

Accurate modeling of static power is challenging, as it depends on both voltage and temperature. Notably, static power is not equivalent to the system's idle power consumption: When the platform is idle (executing no applications), power consumption is reduced due to

<sup>2</sup> https://www.ti.com/product/INA231

power optimization techniques like power and clock gating, where parts of the processor are powered down or clock signals are disabled to save energy [154].

To estimate the static power, we apply regression models to correlate measured power and the number of active cores. By extrapolating to zero active cores, we can approximate the system's static power consumption [80]. By distinguishing between static and dynamic power, we can avoid overestimating energy consumption when aggregating results from multiple applications.

#### 2.1.4 Notation

This thesis employs a consistent and intuitive notation system to describe various elements in the system model, problem formulations, and algorithm descriptions. The notation is designed to resemble familiar programming concepts to readers.

- Objects and Attributes: An object X with specific attributes is denoted as X⟨a<sub>1</sub>, a<sub>2</sub>,..., a<sub>n</sub>⟩, where a<sub>1</sub>, a<sub>2</sub>,..., a<sub>n</sub> are the attributes of the object X. In some cases, objects may be annotated with contextual information, to indicate, for example, their relationship to another object, e.g., X<sup>C</sup>⟨...⟩, where C is an abstract context. For simplicity, the object can be referred to as X, with its definition indicated by :=, i.e., X := X<sup>C</sup>⟨a<sub>1</sub>, a<sub>2</sub>,..., a<sub>n</sub>⟩.

- Accessing Attributes: Attributes of an object X are accessed using the square brackets, denoted as X[a<sub>i</sub>] for the attribute a<sub>i</sub>. This notation is analogous to accessing elements in a data structure.

- *Derived Information*: Some objects may have associated derived values or other related information, which are accessed similarly to attributes. These derived values are also accessed using square brackets and are defined using :=. For example, given an object X with two parameters t<sub>st</sub> and t<sub>fin</sub> representing the start and finish times, i.e., X := X⟨t<sub>st</sub>, t<sub>fin</sub>⟩. A derived value, such as the duration *d*, can then be defined as:

$$X[d] \coloneqq X[t_{\rm fin}] - X[t_{\rm st}]$$

#### 2.2 SYSTEM MODEL

This section provides formal definitions for the architecture, application, and mapping models that serve as the foundation for the approaches presented in this thesis.

#### 2.2.1 Architecture

A Heterogeneous Multi-core Architecture (HMA) consists of processing elements of different types, each exhibiting distinct characteristics, as well as the interconnection mechanisms that enable communication between them.

**Definition 2.1** (Processing Element Type). A *processing element type*  $\Omega$  represents a class of computational units that are instantiated, possibly multiple times, in the HMA. Each processing element type is characterized by its *Instruction Set Architecture* (ISA), performance-energy cost model, and other hardware attributes such as the number of hardware threads if it supports Simultaneous Multithreading (SMT). Formally, a processing element type is defined as  $\Omega := \Omega \langle isa, cm, X \rangle$ , where:

- isa specifies the underlying ISA used by the processing element type.

- cm is an abstract *cost model* specifying power consumption and performance characteristics.

- *X* is a set of additional attributes providing information about the processing element type. For example,  $x_{smt} \in X$  specifies the number of simultaneous hardware threads.

Different processing element types can share the same ISA while differing in other characteristics. With appropriate OS support, a task can be migrated between processing elements of types  $\Omega_i$  and  $\Omega_j$  if they share the same ISA, denoted as  $\Omega_i \sim \Omega_j$ .

The processing element types available in the HMA are represented as a finite sequence  $(\Omega_1, \Omega_2, ..., \Omega_{|(\Omega_i)|})$ , or concisely as  $(\Omega_i)$ , where  $|(\Omega_i)|$  is the number of processing element types.

Each processing element type  $\Omega$  could represent either a generalpurpose processor core or an application-specific accelerator. Where needed, we explicitly distinguish between them.

**Definition 2.2** (Processing Element). A *processing element*  $\psi$  is an instance of a given processing element type  $\Omega$ , denoted as  $\psi := \psi \langle \Omega \rangle$ . It inherits the ISA, cost model, and attributes from its processing element type  $\Omega$ . The set of all processing elements in the HMA is denoted  $\Psi$ .

Although the performance-energy cost model  $\Omega[cm]$  is left abstract, we may denote specific power consumption metrics for processing elements  $\psi$  where needed. Specifically, for a processing element  $\psi$ , we denote  $\psi[P_{\text{static}}]$ ,  $\psi[P_{\text{dynamic}}]$  and  $\psi[P]$  as the static, dynamic and total power consumption, respectively.

**Definition 2.3** (Platform). A *platform*  $\mathcal{P}$  for an HMA is defined as  $\mathcal{P} \coloneqq \mathcal{P} \langle \Psi, \mathcal{IC} \rangle$ .  $\Psi$  is the set of processing elements available in the platform and  $\mathcal{IC}$  is an abstract interconnection model characterizing inter-processor communication.

For convenience, let  $\mathcal{P}[\omega_i]$  denote the number of processing elements of type  $\Omega_i$ , i.e.,

$$\mathcal{P}[\omega_i] \coloneqq |\{\psi \in \mathcal{P}[\Psi] \mid \psi[\Omega] = \Omega_i\}| \tag{2.4}$$

Let  $\mathcal{P}[\vec{\omega}]$  denote the *resource vector* of the platform  $\mathcal{P}$ :

$$\mathcal{P}[\vec{\omega}] \coloneqq \left[\mathcal{P}[\omega_1], \mathcal{P}[\omega_2], \dots, \mathcal{P}[\omega_{|(\Omega_i)|}]\right]^\top$$

(2.5)

This thesis focuses on HMAs such as ARM big.LITTLE (Figure 1.1) or the Intel Alder Lake and Raptor Lake families (Figure 1.2). These systems feature two types of processor cores: high-performance cores (referred to as "big" in ARM, and "P-core" in Intel) and energy-efficient cores (referred to as "LITTLE" in ARM and "E-core" in Intel).

In the proposed algorithms, we assume that all cores of the same type are symmetrical from an interconnection point of view. This assumption is valid for the ARM big.LITTLE platform, which features a single cluster for big cores and a single cluster for LITTLE cores. For Intel's architecture, this assumption is partially true: while each P-core is located in its own cluster, E-cores are grouped into several clusters with four E-cores per cluster. The difference lies in the fact that two E-cores within the same cluster can communicate starting via the L2 cache (which is the closest shared cache level), while communication between E-cores in different clusters begins through the L3 cache.

#### 2.2.2 Application

The HMA executes multiple applications that may vary in their MoC. In addition to information about application components (tasks or threads), applications may also provide a way to control their internal configuration through so-called *adaptivity knobs*. By controlling these adaptivity knobs, the RM can change the application topology, the degree of parallelization, the algorithms used, and more. Along with resource allocation, the RM may leverage these knobs to better adapt the application to the current workload.

This section defines an abstract application model that allows the formulation of the application mapping problem in a general way.

**Definition 2.4** (Application). An *application* is a tuple  $A := A \langle \mathcal{M}, \Gamma, \mathcal{V} \rangle$ , where

- *M* is an abstract model of the application.

- Γ is a set of configuration parameters.

• *V* is a set of *application components* (e.g., tasks, processes, threads) that need to be mapped.

A *configuration*  $\gamma$  is an assignment of values to the configuration parameters in  $\Gamma$ . For each configuration  $\gamma$ , the corresponding set of active application components is denoted by  $\mathcal{V}_{\gamma} \subseteq \mathcal{V}$ . The set of all applications is denoted by  $\mathcal{A}$ .

This definition deliberately separates the application parameters into configuration parameters and application components. The *configuration parameters* specify the internal settings of the application, such as the degree of parallelism or algorithmic choices. The *application components* represent the computational elements (e.g., tasks or threads) that need to be mapped onto the platform's processing elements.

As an example, consider a simple parallel application where the configuration parameter is the number of threads  $\Gamma = \{n_{\text{threads}}\}$ . A specific configuration  $\Gamma = \{n_{\text{threads}} = k\}$  determines the number of threads used by the application. The set of application components  $V_{\gamma}$  would then consists of *k* threads that need to be mapped, i.e.,  $|V_{\gamma}| = k$ .

2.2.3 Mapping

As discussed in Section 2.1.1, mapping can be performed either statically or dynamically. This work focuses on static assignments of tasks to processing elements, which can be defined formally as follows.

**Definition 2.5** (Mapping). A *mapping*  $\mu$  for application  $A\langle \mathcal{M}, \Gamma, \mathcal{V} \rangle$  with a selected application configuration  $\gamma$  on a platform  $\mathcal{P}\langle \Psi, \mathcal{IC} \rangle$  is a specific assignment of each application component  $v \in A[\mathcal{V}_{\gamma}]$  to exactly one core  $\psi \in \mathcal{P}[\Psi]$  in the HMA, i.e.,

$$\mu: A[\mathcal{V}_{\gamma}] \to \mathcal{P}[\Psi] \tag{2.6}$$

The set of processing elements utilized by the mapping is referred to as the *allocation*  $\mu[\Psi]$ , defined as:

$$\mu[\Psi] \coloneqq \{\psi \mid \exists v \in A[V_{\gamma}] : \psi = \mu(v)\}$$

(2.7)

The *resource vector*  $\mu[\vec{\omega}]$  specifies how many instances are allocated per processing element type:

$$\mu[\vec{\omega}] \coloneqq \left[\mu[\omega_1], \dots, \mu[\omega_{|(\Omega_i)|}]\right]^\top$$

(2.8)

where

$$\mu[\omega_i] \coloneqq |\{\psi \in \mu[\Psi] \mid \psi[\Omega] = \Omega_i\}|$$

(2.9)

#### 2.3 MAPPING OF DATAFLOW APPLICATIONS

Building upon the system model introduced in the previous section, this section discusses dataflow Models of Computation (MoCs), which are common application models for streaming applications used in embedded systems. These models naturally represent the flow of data between computational components [107]. Particularly, the section introduces common MoC such as Synchronous Dataflow (SDF), and Kahn Process Network (KPN). We define these dataflow MoCs, discuss their mapping onto platforms, and outline the trace-based simulation used for performance and energy analysis.

#### 2.3.1 Dataflow Models of Computation

Dataflow Models of Computation (MoCs) have gained momentum in the embedded domain, especially for describing streaming and signal processing applications. These models represent computations as directed graphs where the nodes denote computational tasks, and the arcs represent communication channels [107]. Depending on the specific model, these nodes may be referred to as *actors* or *processes*. Each node performs computations based solely on its input values.

Dataflow models have become attractive for several reasons: they explicitly expose parallelism, are well-suited for graphical programming — a common specification paradigm for signal processing algorithms — and the properties of the underlying MoC enable tools to perform analysis and compile the specifications into both software and hardware [37].

Various dataflow models have been proposed for embedded programming, each offering different trade-offs between expressiveness and analyzability. Examples include *Synchronous Dataflow* (SDF) [109], *Cyclo-Static Dataflow* (CSDF) [21], *Boolean Dataflow* (BDF) [108], *Dynamic Dataflow* (DDF) [33], *Process Network* (PN) and *Kahn Process Network* (KPN) [91].

#### 2.3.1.1 Synchronous Dataflow

*Synchronous Dataflow* (SDF), introduced by Lee and Messerschmitt [109], is a dataflow model where the nodes, called *actors*, have the amount of data produced and consumed by each actor firing fixed and known at compile time. The execution of an SDF (*firing*) is controlled by data in its edges; each actor executes or *fires* once it has enough tokens in its input channels. This deterministic behavior makes SDF models statically analyzable: properties such as deadlock-freedom, bounded memory usage, and throughput can be analyzed at design time, making SDF suitable for real-time and resource-constrained applications.

If each actor in SDF consumes and produces exactly one token per firing, the graph is referred to as a *Homogeneous SDF* (HSDF). Any SDF graph can be transformed into an equivalent HSDF graph [186]. Acyclic HSDF (i.e., those without cycles) are structurally equivalent to Directed Acyclic Graphs (DAGs) and can effectively model *task graphs*.

#### 2.3.1.2 Kahn Process Networks

*Kahn Process Network* (KPN), first introduced by Gilles Kahn [91], is a more general and expressive Model of Computation (MoC). In this model, each node executes concurrently as a separate *process*, typically a non-terminating program that reads data tokens from input unbounded First In, First Out (FIFO) channels and writes data tokens to output unbounded FIFO channels. Unlike actors in dataflow models such as SDF, processes in KPN do not have firing semantics; instead, they are either *ready* to execute or *blocked* waiting for input. All processes execute simultaneously [110].

Communication between processes is characterized by *blocking reads* and *non-blocking writes* (also referred as Kahn-MacQueen execution semantics [92]). A process attempting to read from an empty channel will block until data becomes available, whereas writing to a channel is non-blocking as channels are assumed to be unbounded in size.

Importantly, processes cannot check whether data is available on a channel without attempting to read from it. Due to this restriction and the deterministic behavior of each process, the entire KPN is also deterministic. Regardless of the relative speeds of processes or communication delays, the overall system behavior remains predictable and consistent for any given set of input sequences.

KPNs are Turing-complete, meaning they can represent any computation that a Turing machine can perform [33]. This makes them expressive model and capable of representing complex applications. Task graphs and SDF can be considered as restrictions of Kahn Process Networks [107].

Relating KPNs to the application model, defined earlier (Definition 2.4), we observe that for a KPN, the application model  $\mathcal{M}$  is a directed multigraph (V, E), where V is the set of processes and E is the set of unbounded FIFO channels connecting them. This graph encapsulates the computational structure and data dependencies of the application. Since the structure and behavior of the KPN are fixed, there are no tunable parameters, thus,  $\Gamma = \emptyset$ . The set of application components  $\mathcal{V}$  consists of all the processes in the KPN that need to be mapped onto processing elements in the platform.

However, in practical implementations channels cannot be truly unbounded due to physical memory limitations. As a result, channels are implemented as bounded FIFO [143]. This introduces the possibility of *blocking writes*: If a channel is full when a process attempts to write, the process must block until space becomes available. This deviation from the theoretical model can introduce deadlocks and requires careful application design and buffer size determination to avoid such issues.

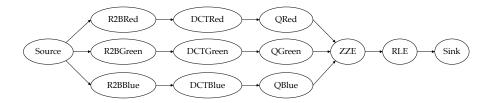

As an example, Figure 2.2 depicts the implementation of a JPEG Image Encoding application [201] as a KPN graph. The Source node reads the input pixel data and distributes the RGB components to the R2BRed, R2BGreen, and R2BBlue processes. These R2B (Row-To-Block)

Figure 2.2: JPEG Image Encoding application as a KPN graph

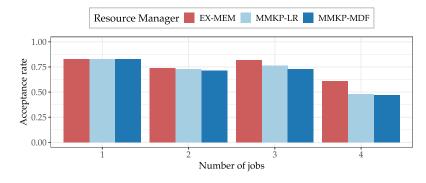

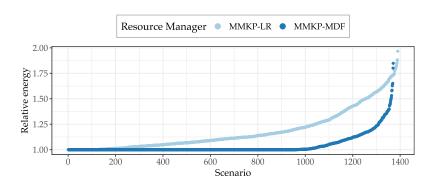

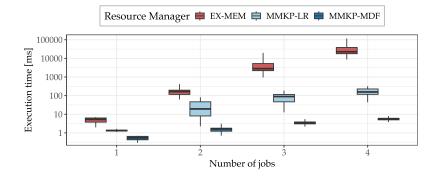

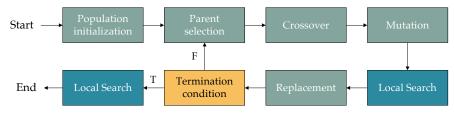

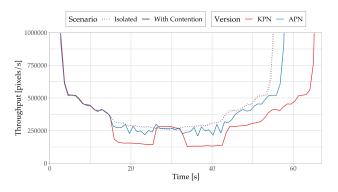

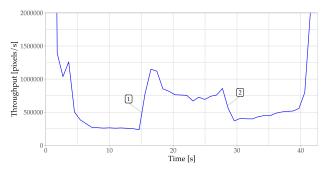

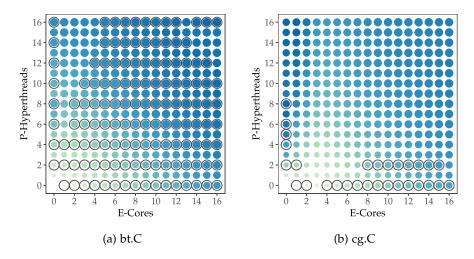

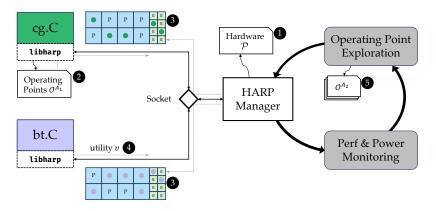

processes convert the pixel data into  $8 \times 8$  blocks for each color channel. The DCT nodes then transform the blocks from the spatial domain to the frequency domain using the *Discrete Cosine Transform*. Quantization is applied by QRed, QGreen, and QBlue, reducing the precision of the DCT coefficients. The *Zig-Zag Encoding* (ZZE) process reorders the quantized coefficients into a one-dimensional array, which is further compressed by RLE through the *Run-Length Encoding* algorithm. Finally, Sink prepares the compressed data for output.